''Año de la lucha contra la corrupción y la impunidad".

Laboratorio N° 12

Circuitos Digitales

Matriz de Leds

Alumno(s)

|

Nota

|

|

Grupo

|

||

Ciclo 2C5

|

Electrónica

y Automatización – Circuitos Digitales

|

|

Fecha de

entrega

|

||

I. CAPACIDAD

TERMINAL

●

Identificar

las aplicaciones de la Electrónica Digital.

●

Describir

el funcionamiento de las unidades y dispositivos de almacenamiento de

información.

●

Implementar

circuitos de lógica combinacional y secuencial.

II. COMPETENCIA

ESPECIFICA DE LA SESION

●

Implementación

de Registros en Serie

●

Contador

en Anillo con Registro serie

●

Identificación

de terminales y prueba de Matriz de Leds

CONTENIDOS A

TRATAR

●

Registros

Series

●

Contador

en Anillo

●

Matriz

de Leds.

IV. RESULTADOS

●

Diseñan

sistemas eléctricos y los implementan gestionando eficazmente los recursos

materiales y humanos a su cargo.

V. MATERIALES

Y EQUIPO

●

Entrenador

para Circuitos Lógicos

●

PC

con Software de simulación.

●

Guía

de Laboratorio. El trabajo se desarrolla de manera GRUPAL.

VI. REPASO

DEL LABORATORIO ANTERIOR

●

Contadores

especiales y Reductores de Frecuencia.

VII. FUNDAMENTO

TEÓRICO

●

Revise

los siguientes enlaces:

●

REGISTROS

EN SERIE

●

CONTADORES

EN ANILLO:

TEORIA DE MATRIZ DE LEDS:

Matriz de Leds

- Una matriz de leds es un display formado por multiples leds, en una distribucion rectangular. Existen distintos tamaños, el mas abitual es el de 8x8. Estos se dividen en filas y columnas claramente se tiene que ver con anterioridad la posicion de los Anodos y Catodos para realizar cualquier trabajo.

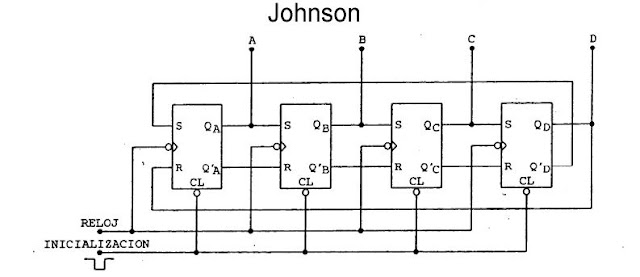

- Contador en anillo. Constituye un registro de desplazamiento en el cual la entrada del 1er Flip-Flops esta condicionada por la salida del ultimo, constituyendo así una cadena cerrada.

- La información introducida inicialmente circula permanentemente por los biestables sin perderse.

- si al comienzo un biestable es puesto en "1" y el resto en "0" (lo cual se logra con las entradas asincrónicas Set y Reset de cada Flip-Flop).

- En contador en anillo funciona pasándose de Flip- Flop a Flip-Flop un unico bit. Esto quiere decir que, en cualquier instante del proceso de conteo, solo un Flip-Flop tiene su salida Q=1. Esto provoca que el contador en anillo sea el contador mas fácil de decodificar.De hecho, sabiendo que el Flip-Flop esta a uno, conocemos en que estado se encuentra el contador.

Implementacion de Contador Jhonson,(SOFTWARE PROTEUS):

Video Tutorial Explicando lo Realizado en Laboratorio:

Observaciones y Conclusiones:

- Faltaba Cables para la realización del Laboratorio.

- A realizar una implementación de registros en serie.

- A realizar y entender el comportamiento de un contador en anillo con registro serie.

- A identificar de terminales y prueba de Matriz de leds.

- Describir el funcionamiento de las unidades y dispositivos de almacenamiento de información.

- Implementar circuitos de lógica combinacional y secuencial.

¿Que he aprendido de esta experiencia?